Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

2024-04-01

Επί του παρόντος, οι σερβοκινητήρες σε εγχώρια εργαλεία CNC είναι γενικά εξοπλισμένα με αυξητικούς κωδικοποιητές, ενώ η ακρίβεια των αυξητικών κωδικοποιητών δεν είναι πολύ υψηλή και η έξοδος είναι παράλληλα σήματα. Για να βελτιωθεί η ακρίβειά του, είναι απαραίτητο να αυξηθεί ο σχεδιασμός του κωδικοποιητή. Δυσκολία και αύξηση της παραγωγής παράλληλων σημάτων, η οποία δεν ευνοεί την επικοινωνία μεγάλων αποστάσεων μεταξύ της σερβο μονάδας και του κωδικοποιητή. Ο απόλυτος κωδικοποιητής χρησιμοποιείται, εκτός από το ότι η ακρίβειά του είναι αρκετές φορές υψηλότερη από αυτή του αυξητικού κωδικοποιητή. Η σειριακή επικοινωνία υψηλής ταχύτητας εξοικονομεί γραμμές επικοινωνίας για επικοινωνία μεγάλων αποστάσεων. Στο άλλο άκρο του κωδικοποιητή, το CPLD και ο απόλυτος κωδικοποιητής χρησιμοποιούνται για σειριακή επικοινωνία υψηλής ταχύτητας. Στη συνέχεια, το CPLD μετατρέπει τις πληροφορίες που λαμβάνεται σε παράλληλη μετάδοση δεδομένων. Το DSP στη μονάδα σερβοετηρίων εκτελεί αριθμητικό έλεγχο. Αυτό το έγγραφο θα δώσει στο λογισμικό και το σχεδιασμό υλικού της σειριακής επικοινωνίας υψηλής ταχύτητας μεταξύ CPLD και απόλυτου κωδικοποιητή .

σχεδιασμός υλικού

Το υλικό αποτελείται κυρίως από τρεις ενότητες: τροφοδοτικό ρεύματος, CPLD και τα περιφερειακά κυκλώματα και το κύκλωμα διασύνδεσης απόλυτου κωδικοποιητή.

Μονάδα ισχύος

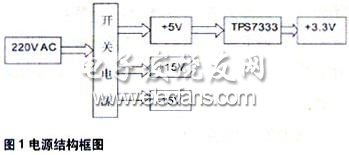

Η μονάδα ισχύος αποτελείται από ένα κύκλωμα τροφοδοσίας μεταγωγής και ένα τσιπ τροφοδοσίας DC/DC, όπως φαίνεται στο σχήμα 1.

Η τροφοδοσία μεταγωγής στο σχήμα μετατρέπει την τάση πλέγματος AC 220V σε +5V, +15V, -15V. Η τροφοδοσία μεταγωγής μπορεί να φιλτράρει διάφορες παρεμβολές στο ηλεκτρικό δίκτυο και ο μετασχηματιστής στην τροφοδοσία μεταγωγής θα είναι 220V AC και η έξοδος είναι + 5V, + 15V, -15V είναι απομονωμένη, το εσωτερικό κύκλωμα χρησιμοποιεί επίσης TL431 για να ρυθμίσει το Πλάτος παλμού αγωγιμότητας του σωλήνα διακόπτη, έτσι ώστε η ρύθμιση αντι-παρεμβολής, ασφάλειας, σταθερότητας και τάσης της τροφοδοσίας μεταγωγής είναι καλύτερη. Το TPS7333 είναι ένα τσιπ DC/DC. Η τάση +5V DC μετατρέπεται σε σταθερή τάση DC +3.3V για χρήση από το CPLD. Το TPS7333 έχει καλύτερη απόδοση μετατροπής, αξιοπιστία και ρύθμιση τάσης. Μπορεί να χρησιμοποιηθεί στην περιοχή τάσης +3.77V- +10V. Η μετατροπή +3.3V προκαλεί την καύση του CPLD λόγω της τάσης εισόδου να είναι υπερβολικά υψηλή.

Το CPLD και οι μονάδες του περιφερειακού κυκλώματος

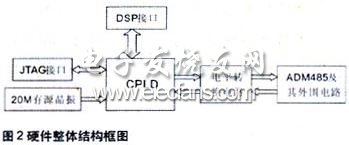

Το CPLD και οι μονάδες του περιφερειακού κυκλώματος αποτελούνται κυρίως από CPLD, CPLD προγραμματισμό Download Interface Circuit (Interface JTAG), κύκλωμα διασύνδεσης DSP, ενεργό κρυστάλλινο ταλαντωτή, κύκλωμα μετατροπής επιπέδου και ADM485 και τα περιφερειακά κυκλώματα του (Circuit Interface για την επικοινωνία με τον κωδικοποιητή) . Σχήμα 2).

Αυτός ο σχεδιασμός CPLD χρησιμοποιεί το EPM570T144C5 της Altera, το οποίο ανήκει στο Max II της Altera. Το Max II είναι χαμηλότερο στο κόστος από το Max I και καταναλώνει λιγότερη ισχύ. Η συσκευή διαθέτει περισσότερα μακρο κύτταρα και η καθυστέρηση της συσκευής ελέγχεται εντός 6 ns. Με υψηλό κόστος απόδοσης, το EPM570T144C5 έχει 570 μακροκύτταρα. Ο αριθμός των ακίδων στο τσιπ είναι 144, εκ των οποίων οι 116 είναι διαθέσιμοι θύρες εισόδου/εξόδου, οπότε οι πόροι αυτού του τσιπ είναι επαρκείς. Το CPLD είναι κυρίως υπεύθυνο για τη σειριακή επικοινωνία υψηλής ταχύτητας με τον απόλυτο κωδικοποιητή και ελέγχεται από την εντολή DSP για την προώθηση των δεδομένων κωδικοποιητή και άλλων πληροφοριών στο DSP παράλληλα.

Η διασύνδεση JTAG χρησιμοποιείται κυρίως για τη λήψη του εκτελέσιμου αρχείου στο CPLD, την εγκατάσταση του περιβάλλοντος ανάπτυξης της εταιρείας Altera - Quartus II στον υπολογιστή και καταρτίζετε το γραπτό πρόγραμμα VHDL σε αυτό το αναπτυξιακό περιβάλλον για να διασφαλιστεί ότι η συλλογή δεν είναι χωρίς σφάλματα χωρίς σφάλματα και η λειτουργία εφαρμόζεται. Συνδέστε το καλώδιο λήψης στη διεπαφή JTAG και κατεβάστε την πλακέτα CPLD μέσω του εργαλείου λήψης προγραμματισμού που παρέχεται από το Quartus II.

Η διεπαφή DSP αποτελείται από 8 γραμμές δεδομένων, 3 γραμμές διευθύνσεων και 1 γραμμή ελέγχου. Οι 8 γραμμές δεδομένων είναι υπεύθυνες για τη μεταφορά των δεδομένων κωδικοποιητή και άλλων πληροφοριών. Οι 3 γραμμές διευθύνσεων είναι υπεύθυνες για τη μετάδοση εντολών DSP και την αποκωδικοποίηση του τερματικού CPLD. Το CPLD μεταδίδει τα δεδομένα κωδικοποιητή ή άλλες πληροφορίες στο DSP μέσω 8 γραμμών δεδομένων σύμφωνα με την εντολή αποκωδικοποίησης. Η γραμμή ελέγχου ολοκληρώνει κυρίως τον σύγχρονο έλεγχο του CPLD και του DSP.

Ο ενεργός ταλαντωτής 20M Crystal παρέχει κυρίως ένα ρολόι αναφοράς για το CPLD. Κάτω από την οδήγηση του σήματος ρολογιού, το CPLD δημιουργεί ρυθμό Baud 2,5Mb/s για να επικοινωνήσει με τον κωδικοποιητή και δημιουργεί ρολόι 10M Hz για ορισμένα σήματα ελέγχου λογικής. Η παροχή συχνότητας ρολογιού 20Μ Hz απαιτεί τάση DC 3.3V από την τροφοδοσία ρεύματος.

Το κύκλωμα μετατόπισης επιπέδου είναι κυρίως υπεύθυνο για τη μετατροπή των 3,3V σε 5V ή 5V σε 3,3V, επειδή οι θύρες πυρήνα και εισόδου/εξόδου του CPLD απαιτούν τάση τροφοδοσίας 3,3V, η οποία απαιτείται για ADM485 και απόλυτες κωδικοποιητές. Τόσο η τάση τροφοδοσίας όσο και το κύκλωμα του οδηγού θύρας εισόδου/εξόδου είναι 5V, επομένως είναι απαραίτητο να μετατρέψετε 3,3V σε 5V ή 5V σε 3,3V με το chip μετατροπής επιπέδου LVC4245A.

Το ADM485 και τα περιφερειακά του κυκλώματα είναι η σύνδεση υλικού μεταξύ της CPLD και της απόλυτης επικοινωνίας υψηλής ταχύτητας κωδικοποιητή. Η τάση εργασίας του ADM485 είναι 5V και η μέγιστη ταχύτητα επικοινωνίας είναι 5MB/s. Η χρήση δύο τσιπ ADM485 για επικοινωνία σύνδεσης μπορεί να βελτιώσει την ικανότητα κατά της παρεμβολής στη γραμμή επικοινωνίας και η μακρύτερη απόσταση μετάδοσης μπορεί να φτάσει τα 1,2 χιλιόμετρα. Το περιφερειακό κύκλωμα φαίνεται στο σχήμα 3. Το δεξί μισό της διακεκομμένης γραμμής ανήκει στο περιφερειακό κύκλωμα του απόλυτου κωδικοποιητή. Οι αντιστάσεις Pull-Up και Pull-Down είναι 1k ohms, η αντίσταση περιορισμού ρεύματος είναι 220 ohms και το ADM485 SDAT είναι ο ακροδέκτης εξόδου δεδομένων. Το ADM485 είναι το SRQ είναι ο πείρος εισόδου δεδομένων, το DE του ADM485 είναι ο εξωτερικός πείρος ελέγχου, αυτός ο ακροδέκτης ελέγχεται από το CPLD. Δεδομένου ότι το πρωτόκολλο επικοινωνίας RS-485 είναι μισό διπλό, το ADM485 μπορεί να βρίσκεται μόνο σε κατάσταση αποστολής δεδομένων ή λήψης δεδομένων. Όταν το ADM485 είναι DE High, το ADM485 βρίσκεται σε κατάσταση εξόδου δεδομένων (δηλαδή, η CPLD λαμβάνει δεδομένα). Όταν το DE του ADM485 είναι χαμηλό επίπεδο, το ADM485 βρίσκεται σε κατάσταση εισόδου δεδομένων (δηλαδή, η CPLD στέλνει δεδομένα).

Μοιραστείτε το στο:

Αποστολή Εξεταστική

Ms. carol Dong

Τηλ.:86-431-85543703

Fax:86-431---88634119

Κινητό τηλέφωνο:+8613894866263

ΗΛΕΚΤΡΟΝΙΚΗ ΔΙΕΥΘΥΝΣΗ:sales@encoders.com.cn

Διεύθυνση:333Feiyue Donglu, Changchun City, Jilin Province. China, Changchun, Jilin

ιστότοπο για κινητά

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.